下图中所包含的演示资料则源自由Intuitive Cognition Consulting负责人Dave Eggleston所作出的《3D XPoint MRAM与RRAM:未来就在当下》演讲。

3D XPoint内存晶圆近照

本届闪存记忆体峰会上的一次主题演讲对英特尔/美光联合打造的3D XPoint内存技术作出了相关猜测——包括这项技术的具体定义以及英特尔会在未来如何加以运用。我们就其中的部分内容向知识渊博的从业专家进行了咨询,并以此为基础提出自己的观点——同样围绕这两点,该技术究竟算是什么、未来又将如何发展。

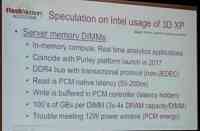

本月13号星期四在301-C会话环节中作出的这次演讲题为《后闪存生活——新型非易失性内存技术(新技术追踪)》。下图中所包含的演示资料则源自由Intuitive Cognition Consulting负责人Dave Eggleston所作出的《3D XPoint MRAM与RRAM:未来就在当下》演讲。

顺带一提,目前大家还无法直接从闪存记忆体峰会的官方网站上获取到这些资料——确实有点遗憾。也许再过一、两天,相关信息才会正式上线。

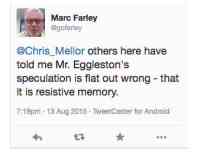

Tegile公司的Marc Farley亲自参加了这一主题演讲,并就相关内容此发表了以下推文。

可以看到,Eggleston认为XPoint属于经过品牌调整的相变记忆体(简称PCM)。上图中的演示内容截取自Dave Eggleston的演示资料,其中包括英特尔公司未来可能采取的XPoint内存使用方式。

下面通过放大图一起来看更多细节信息:

本届闪存记忆体峰会2015大会上的Dave Eggleston演示文稿

我曾经与某位知识渊博的业内人士就此进行过交流,对方认为XPoint内存不应被看作是PCM的品牌调整结果。XPoint确实在物理流程当中使用了相变机制,但其主要革新成果体现在底层存储单元材料以及选择器的设计层面。业界普遍认为这一成果要远远领先于东芝以及三星的STT-MRAM(即自旋矩磁性RAM)方案或者(根据这位业内人士的说法)惠普迟迟拿不出实际样品的忆阻器技术。

XPoint内存是一项行之有效的技术方案,而且在成本/存储密度方面拥有相当出色的市场吸引力。总而言之,这是一项革命性的开发成果。

这份演示文稿指出,英特尔公司可能会将XPoint引入到服务器内存DIMM当中。其具体时间可能会与英特尔计划于2017年年内推出的,代号为Purley的至强服务器CPU保持一致。我们的这位专家指出,目前可以确定其将配合新型协议采用DDR4总线,而且显然会针对Read公司目前已经确定的50至200纳秒PCM原生延迟水平作出大量调整工作。

与Eggleston发布的演示资料相比较,XPoint的实际写入缓冲性能明显要出色得多。

目前每DIMM超过100 GB传输带宽已经得到确认,而且12瓦的预定功率窗口设计也表示压力不大。

有鉴于此,我们可以预计在2017年年内迎来速度更为惊人的服务器方案——这不仅是由于标准的CPU更新换代,同时也受到了存储性能水平的巨大推动。通过将数据保存在以DIMM形式存在的大量3D XPoint内存模块当中,我们将能够为数量日益增长的计算核心提供充沛的数据供应。快些到来吧,美好的新时代!

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。