采用开发的桥接芯片占用面积小,功耗低,与传统的无桥芯片方法相比,可以连接更多的闪存芯片和更少的高速信号线。

中存储网消息,东芝Me mory 公司近日公布,公司开发了一种桥接芯片,可实现高速和大容量SSD。

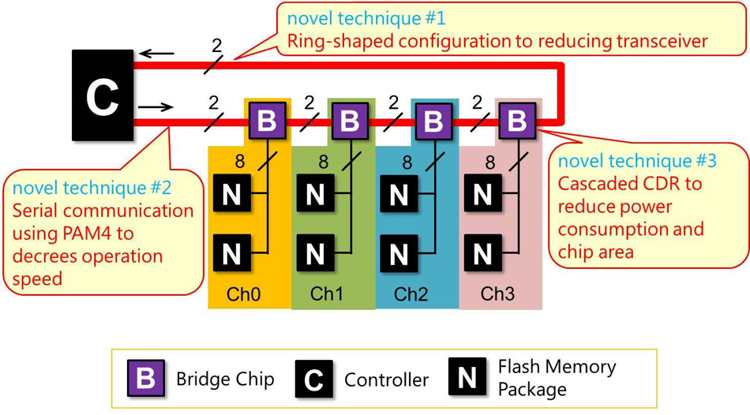

图1使用桥接芯片的连接

采用开发的桥接芯片占用面积小,功耗低,与传统的无桥芯片方法相比,可以连接更多的闪存芯片和更少的高速信号线。该结果于2月20日在加利福尼亚州旧金山举行的2019年国际固态电路会议(ISSCC 2019)上公布。

在SSD中,多个闪存芯片连接到管理其操作的控制器。随着越来越多的闪存芯片连接到控制器接口,运行速度降低,因此可连接的芯片数量有限。为了增加容量,需要增加接口数量,但这导致大量高速信号线连接到控制器,使得在SSD板上实现布线更加困难。

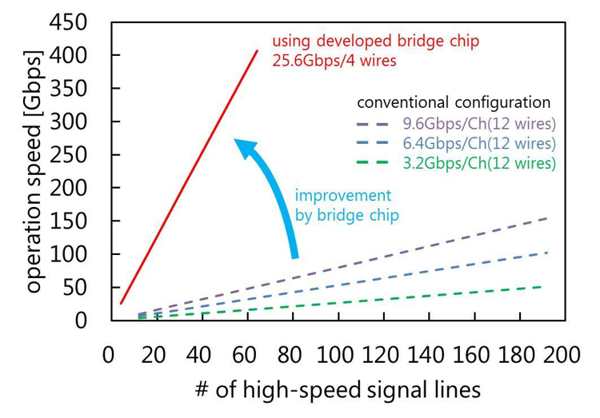

图2桥芯片的改进

该公司通过开发连接控制器和闪存芯片的桥接芯片(图1)克服了这个问题,这三种新技术:菊花链(* 1)连接,包括控制器和环形桥接芯片; 使用PAM 4 (* 2)的串行通信; 以及用于消除桥芯片中的PLL电路(* 4)的抖动(* 3)改进技术。通过使用这些技术,减少了桥接芯片的开销,并且可以仅使用少量高速信号线高速操作大量闪存芯片(图2)。

桥芯片和控制器的环形配置将桥芯片所需的收发器数量从两对减少到一对,实现了桥芯片的芯片面积减小。此外,在控制器和菊花链桥接芯片之间采用PAM 4串行通信可降低桥接芯片(')电路的运行速度,并放宽其所需性能。利用PAM 4的特性来改善抖动特性的CDR (* 5)消除了对桥接芯片中的PLL电路的需要,这也有助于更小的芯片面积和更低的功耗。

原型桥接芯片采用28nm CMOS工艺制造,并通过连接四个桥芯片和环形菊花链中的控制器来评估结果。这证实了所有桥接芯片和控制器在25.6Gb / s下的PAM 4通信的令人满意的性能,并且还可以获得小于10 -12的BER (* 6)。

展望未来,该公司将继续开发工作,通过进一步提高桥接芯片性能,同时降低芯片面积和功耗,实现高速,大容量存储。

注释:

(* 1)菊花链:连接方案,其中多个芯片按顺序连接在一起

(* 2) PAM 4:4级脉冲幅度调制(它包含4值数据)

(* 3)抖动:波动时钟或信号波形的时域

(* 4) PLL:锁相环(产生精确参考信号的电路)

(* 5) CDR:时钟数据恢复(从接收信号中恢复数据和时钟的电路)

(* 6) BER:误码率(较低的值是更好的性能)

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。