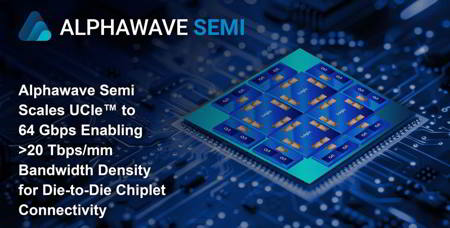

通过其 Gen3 64Gb UCIe IP 彻底改变连接方式,提供超过 20Tbps/mm 的带宽密度,以及超低功耗和延迟。

Alphawave Semi 推出了 业界首个 64Gb 通用小芯片互连高速 (UCIe) Die-to-Die (D2D) IP 子系统,以提供小芯片互连数据速率,为业界超高性能 D2D 连接解决方案设定了新标准。

第 3 代 64Gb IP 子系统建立在最新的 Gen2 36Gb IP 子系统和经过硅验证的 Gen1 24Gb 的成功基础上,采用 TSMC 的 3nm 技术,适用于标准和高级封装。经过硅验证的成功和流片里程碑为 Alphawave Semi 的 Gen3 UCIe IP 子系统产品铺平了道路。

该公司将通过其 Gen3 64Gb UCIe IP 彻底改变连接方式,提供超过 20Tbps/mm 的带宽密度,以及超低功耗和延迟。该解决方案具有高度可配置性,支持多种协议,包括 AXI-4、AXI-S、CXS、CHI 和 CHI-C2C,以满足 HPC、数据中心和 AI 应用中分解系统对高性能连接日益增长的需求。

该设计符合最新的 UCIe 规范,并具有可扩展的架构,具有高级可测试性功能,包括实时每通道健康监测,使其成为强大的基础,并实现开放和可互操作的小芯片生态系统。

UCIe D2D 互连有助于实现一系列标准和新兴的小芯片连接场景。常见用途包括通过 UCIe 的流功能链接计算小芯片以实现低延迟、一致的连接,以及使用带有 PCIe、CXL 或以太网的 UCIe 接口将计算连接到 I/O 小芯片。此外,光重定时器可以利用 UCIe 小芯片架构,通过光引擎建立可靠、低延迟的光 I/O 链路,从而增强系统外连接。这支持了数据中心和 AI/ML 系统中低功耗、高速解决方案的开发。

对于高性能应用,使用最新的 UCIe 标准创建自定义 HBM 基础芯片是一种尖端方法,它涉及将内存芯片与计算芯片紧密集成,以实现极高的带宽以及组件之间的低延迟。这允许将主晶粒上已经占用的晶粒到晶粒海岸线重新用于内核到内核或内核到 I/O 连接。这种方法极大地优化了 AI 应用程序中的内存事务,其中低功耗和降低延迟是性能差异化因素。

“UCIe 联盟很高兴看到成员实现流片等关键里程碑,这表明 UCIe 规范的采用率越来越高,”UCIe 联盟营销工作组主席 Brian Rea 说。UCIe 是小芯片行业的基石,为高速、低延迟的 die-to-die 互连提供强大的解决方案。通过采用开放标准,我们使行业能够加速创新、缩短上市时间并提供突破性技术。“

Alphawave Semi 定制硅和 IP 高级副总裁兼总经理 Mohit Gupta 表示:“我们在 3nm 技术上以 36 Gbps 的速度成功流片 Gen2 UCIe IP 建立在我们开创性的经过硅验证的 3nm UCIe IP 和 CoWoS 封装的基础上。“这一成就为我们的 64Gb Gen3 UCIe IP 奠定了基础,其目标是在 2025 年为需要最大化海岸线密度以满足关键 AI 带宽需求的客户提供高性能、20 Tbps/mm 吞吐量功能。”

这一成就,以及 Alphawave Semi 早期推出的业界首个经过硅验证的 Gen1 UCIe IP,再次肯定了该公司作为高性能小芯片连接解决方案领导者的快速发展,拥有为超大规模和数据基础设施市场量身定制的全套经过硅验证的连接 IP 子系统。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。