比起其他存储器, RRAM 器件制备工艺很简单, 可以采用溅射、化学汽相淀积、脉冲激光淀积以及电子束蒸发等工艺形成电阻层, 不需要增加专门的设备。

新一代存储技术: 阻变存储器

王源 贾嵩 甘学温

北京大学微电子学研究院, 教育部微电子器件与电路重点实验室, 北京 100871; † E-mail: wangyuan@pku.edu.cn

摘要 阻变存储器具有存储单元结构简单、工作速度快、功耗低、有利于提高集成密度等诸多优点, 受到广泛的关注。作者论述了RRAM 的基本结构和工作原理, 并介绍了三维集成和多值存储等RRAM 新型技术。

关键词 不挥发性存储器; 阻变存储器; 电阻可逆转换; 三维集成; 多值存储

过去几十年里集成电路技术得到突飞猛进的发展, 以集成电路为核心的信息产业已经成为国民经济的支柱产业。特别是半导体存储器在信息产业的增长中起到关键作用。DRAM, SRAM 和Flash存储器已经成为信息产业的核心产品。

由消费类产品驱动的存储器市场需要更高密度、高速度、低功耗、具有不挥发性且价格便宜的存储器产品。到目前为止, Flash 是最成功的高密度不挥发性存储器。但是随着器件尺寸不断缩小,Flash 的发展受到限制, 一方面它的编程电压不能按比例减小, 另一方面随着器件尺寸减小、隧道氧化层减薄, 电荷保持性能下降。 因此, 新的存储技术的研究越来越受到关注, 如铁电存储器(FeRAM)、磁存储器(MRAM)、相变存储器(PRAM)和阻变存储器(RRAM)。 FeRAM 利用铁电材料在电场作用下极化方向反转的特性存储二进制信息[1−2]。FeRAM 具有自极化特性, 当电场去掉后极化特性仍然保持, 因此是一种不挥发性存储。MRAM 利用磁性材料的2 个磁化方向存储二进制信息, 利用电流产生磁场改变材料的磁化方向写入信息[3−5], 在没有外加磁场时材料的磁化方向保持不变, 因此也是不挥发性存储。FeRAM 和MRAM由于需要特殊的材料, 不易与常规CMOS 工艺兼容, 制作成本也比较高, 另外, 读出信号微弱,FeRAM 读操作会破坏原来的“1”信号, 需要数据再生[1], 这些问题影响了它们的应用。PRAM 利用材料在晶态和非晶态的转化, 材料在晶态是低电阻,在非晶态是高电阻, 用这两种状态实现二进制信息的存储, 也是不挥发性存储。但是实现材料的相变需要较大的电流, 例如对于180 nm 工艺的器件, 编程电流在几百微安到1 mA[6], 因此单元中的MOS晶体管尺寸不能太小, 这样就限制了单元尺寸的缩小。RRAM 利用材料电阻率的可逆转换实现二进制信息的存储。由于可以实现电阻可逆转换的材料非常多, 因此便于选择出制备工艺简单且和CMOS工艺兼容的材料。RRAM 存储单元结构简单、工作速度快、功耗低、信息保持稳定、具有不挥发性, 而且易于实现三维立体集成和多值存储, 有利于提高集成密度。表1[7−8]比较了不同类型存储器的主要性能, 可以看出, RRAM 在很多性能方面都有优势。因此, RRAM 将有可能替代DRAM, SRAM 和Flash成为通用存储器, 是未来新一代存储技术的有力竞争者。

1 RRAM 基本原理

Chua[9]1971 年首次从理论上提出忆阻器(memristor)的概念, 这种器件的电阻可以通过施加电压或电流而改变, 因此可以用它的低阻和高阻两种状态存储逻辑“0”和逻辑“1”。 2000 年liu 等[10]报道了用电脉冲感应的电阻可逆转的(electric pulse induced reversible, EPIR)不挥发性存储器件, 他们采用钙钛矿氧化物PCMO(Pt0.7Ca0.3MnO3)作存储电阻, 这就是RRAM。从此, RRAM 的研究吸引了越来越多的关注, 成为新一代存储技术研究的热点。

可以实现电阻可逆转换的材料非常多, 主要有钙钛矿氧化物[7,10]、过渡金属氧化物[11−13]、固态电解质材料[14]、有机材料[15−16]以及其他材料。不过, 对众多的可用于RRAM 的材料会经历一个淘汰选择的过程, 一方面要深入理解材料电阻转变的物理机制,另一方面要考虑材料的制备工艺, 特别要考虑和CMOS 集成电路工艺兼容。到目前为止, 对材料的电阻转变机制还缺乏深入理解, 对电阻转变机制的探讨[11,17−18]以及如何提高器件性能仍是研究的热点。

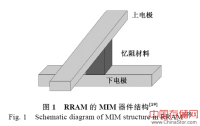

RRAM 采用MIM 结构的存储器件, 结构非常简单, 在上、下电极中间是忆阻材料, 如图1 所示。

当在两个电极之间加一定幅度和一定宽度的脉冲电压, 会使忆阻材料在两个稳定的电阻态转换。也可以用多个幅度较小的窄脉冲实现编程。存储电阻

I-V 曲线如图2[19]所示, 具有典型的回滞特性。曲线分成4 个区域: 高阻态、低阻态和2个转变区, 只有电压幅度超过一定阈值时可以对电阻进行编程或复位, 编程电压的大小及脉宽与材料性能有关。用较小幅度的窄脉冲探测电阻的大小, 进行读操作,由于脉宽和幅度都比较小, 不会改变电阻的状态,因此, 是非破坏性读出。 要得到显著的电阻变化,需要较小的器件尺寸, 因为电阻转变特性与1/D2有关, D 是忆阻材料层的厚度[19]。这也是为什么直到近十几年随着工艺技术的发展RRAM 的研究才更加深入。RRAM 可以获得较大的开关电阻比, 根据最新文献报道, RRAM 的开关电阻比可以超过106~107。

比起其他存储器, RRAM 器件制备工艺很简单, 可以采用溅射、化学汽相淀积、脉冲激光淀积以及电子束蒸发等工艺形成电阻层, 不需要增加专门的设备。有些制备工艺还可以在室温进行, 不需要高温工序。这些都有利于降低成本, 便于和标准CMOS 工艺兼容。甚至可以在完成逻辑电路制作后,仅仅利用后步工序完成存储器件。

图1 RRAM 的MIM 器件结构[19]

Fig. 1 Schematic diagram of MIM structure in RRAM[19]

图2 忆阻器的回滞特性[19]

Fig. 2 Hysteresis characteristics of memristor[19]

2 RRAM 存储单元结构和工作原理

RRAM 存储单元可以采用3 种基本结构, 即0T1R 单元、1D1R 单元和1T1R 单元, 如图3 所示。

还有的研究小组提出了一种叠置的1TXR 单元结构, 这种结构将在3 维存储结构中介绍。下面分别说明0T1R、1D1R 和1T1R 存储单元的结构和工作原理。

2.1 0T1R 单元

图1 所示就是0T1R 单元, 只用一个存储电阻构成一个单元, 电阻的上电极接字线, 电阻的下电极接位线。这种单元结构简单可以实现4F2 的最小单元面积, 而且便于实现三维立体集成。2008 年

图3 RRAM 的3 种基本单元结构

Fig. 3 Schematic diagram of generic RRAM cell

HP 实验室制作出半节距30 nm的MIM结构存储器件, 而当时DRAM 的半节距是59 nm[19]。构成存储阵列时在每条字线和位线上加选择开关, 如图4[8]所示。在编程和读操作时, 通过行译码和列译码选中一条字线和一条位线, 从而选中交叉点的单元,但是这种0T1R单元阵列存在严重的干扰。如图5[20]所示, 如果要读取右下角的高阻单元, 读出电流应该很小, 但是由于周围的3 个单元都是低阻态, 会通过这3 个低阻单元形成较大的干扰电流, 如图5中虚线标出的电流路径, 从而造成读出错误。因此,采用这种0T1R 单元结构需要采用具有自整流特性的忆阻材料, 如Chen 等[8]用硫族化合物Ge2Sb2Te5作电阻, 采用0.18 μm CMOS 工艺制作出4 kbRRAM。

为了减小非选单元引起的干扰, 在操作时对非选中的字线和位线加一定的电压抑制干扰。有两种电压方案, 一种是V/2 方案, 另一种是V/3 方案[8]。V/2 方案如图6(a)所示, 对选中字线加正常操作电压, 选中位线接地, 其余所有非选中的字线和位线都接V/2, 编程(置位)、擦除(复位)和读操作时的V 分别是1.3, 1.0 和1.15 V。这种单元不是用两种极性相反的电压实现置位和复位操作, 复位操作是采用相同极性幅度较低宽度较大的脉冲电压实现。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。