ReRAM初创企业Crossbar公司已经发布了一款来自SMIC的嵌入式ReRAM芯片样品,且其目前正在接受评估。

16纳米?再低。10纳米?再低。Crossbar在制程方面表现出超强的野心。

ReRAM初创企业Crossbar公司已经发布了一款来自SMIC的嵌入式ReRAM芯片样品,且其目前正在接受评估。

SMIC目前正在采用40纳米制程,且有计划进一步开发28纳米制程工艺。但Crossbar公司的设想是至少要将其控制在16纳米到10纳米水平,且随后还要进一步实现缩小。

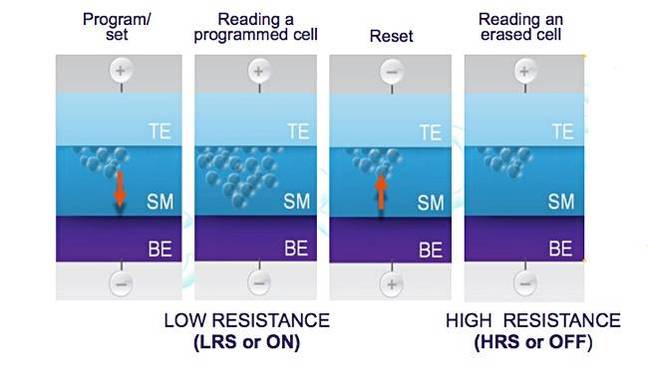

这款芯片设计方案采用非导电非晶硅(简称a-SI)技术。顶部与底部电极之间存在开关层,且该层相对于通过电流的电阻基于离子(银)金属运动。当在两个电极之间施加足够的电压时即可导致电极间形成离子态纳米长丝,而电阻也将因此而改变。

Crossbar公司表示,单一单元可由一个晶体管进行控制,即一晶体管每ReRAM单元——简称为1T1R。各晶体管存在尺寸限制。另外,为了实现成本效益,在各单元皆拥有单元内选择器机制可用于选择或者不选择个别单元的情况下,则单一晶体管最多可控制2000个ReRAM单元——即1TnR模式。

这一方案通过交叉开关机制来实现,其基本思路与3D XPoint内存一致——我们也可以将其称为另一种3D XPoint方案。就目前来看,其中可实现最多16个交叉层级。

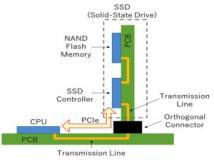

1T1R模式能够提供最低延迟水平,而1TnR模式则拥有最理想的单位区域存储密度。我们可以想象,1T1R模式应该会被用于嵌入式内存应用、演进式缓存; 而1TnR模式则被用于M.2甚至是NVDIMM等形式的SSD等存储驱动器。

Crossbar公司告诉我们,其将ReRAM单元缩小至次10纳米级别的尝试将不会对纳米长丝的形成与撤销产生不利影响,这一点与NAND闪存不同。相比之下,NAND闪存单元若缩小至一定程度,则会导致能够用于保持所施加电荷的电子数量太少,最终致使单元位值衰减。除此之外,Crossbar公司表示其ReRAM芯片相较于NAND闪存在读取延迟上低100化妆品,定稿性能则可提高20倍。该公司指出:“基于ReRAM的SSD产品将提供更低且更为稳定的读取延迟,具体范围在数十微秒水平。”

SSD的随机4K读取延迟可能为150微秒,但缓存与访问堆栈简化将能够降低这一延迟。举例来说,NVMe PCIe SSD的读取延迟在110微秒,而写入延迟则为30到50微秒。据我们了解,美光Optane(3D XPoint)的读取延迟为10微秒,写入延迟则为20微秒。

这意味着ReRAM仍然需要克服一定障碍才能真正获得市场吸引力。

ReRAM还采用字节可寻址机制以取代块可寻址。其设计方案适用于那些“通过移除大部分用于垃圾回收的背景内存访问以显著简化存储控制器复杂度”的小型页面。

Crossbar公司的ReRAM技术在进行编程之前不需要进行任何擦除操作,而且应该比15纳米单元尺寸的2D MLC与TLC NAND拥有更出色的使用寿命。不过我们尚不清楚其使用寿命与尺寸更大的光蚀刻3D NAND相比孰优孰劣。

早在2014年12月,Corssbar公司就表示其已经解决了一项影响到单元内容可读性的电流路径难题。2015年9月,该公司在D轮融资中筹得3500万美元,主要用于该项技术的商业化。而2014年的C轮融资亦有2500万美元进账。该公司将首批生产时间规划在2016年年末。

Crossbar公司将其技术授权至代工厂商,同时亦在与多位潜在合作伙伴探讨推出不同ReRAM内存式芯片的具体方案。

目前,XPoint、ReRAM与NRAM之间的竞争正愈演愈烈,而各供应商及技术初创企业亦纷纷拿出自己的方案以解决DRAM与闪存之间的性能鸿沟。

预计今年晚些时候,Crossbar公司还将公布更多值得关注的新消息。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。