沿着摩尔定律,半导体的工艺尺寸缩小仍在持续,突出的矛盾是由于研发与量产的费用昂贵,能跟进的厂家数量越来越少,以及未来的每两年前进一个工艺制程节点,会从每两年推迟到三年,甚至更长。从尺寸缩小角度,定律可能尚有十年左右的时间。芯片巨头英特尔的1.

沿着摩尔定律,半导体的工艺尺寸缩小仍在持续,突出的矛盾是由于研发与量产的费用昂贵,能跟进的厂家数量越来越少,以及未来的每两年前进一个工艺制程节点,会从每两年推迟到三年,甚至更长。从尺寸缩小角度,定律可能尚有十年左右的时间。

芯片巨头英特尔的10纳米工艺制程一再的“跳票”,表征芯片技术层面追求完美,十分的不易,引起业界的反思。

3纳米坎

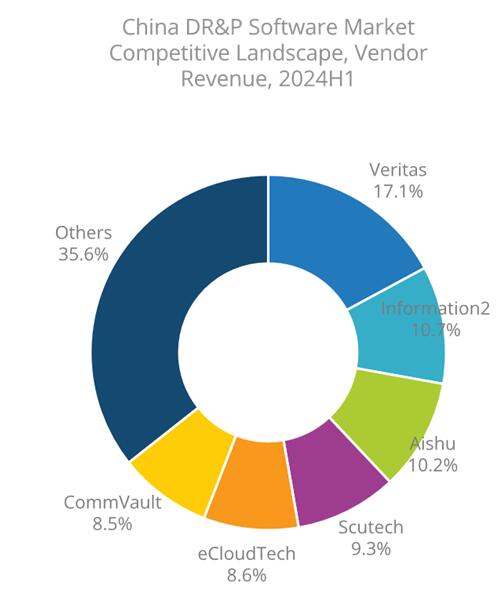

全球半导体从工艺制程角度,仅剩下三家在比拼,英特尔的路径可能有些起伏,导致只剩下两家,分别是台积电与三星,观察总的趋势台积电获得了更大的市场份额,暂时走在前列。

台积电从2018 Q3开始7纳米量产,并占季销售额的10%,估计累积投资达250-300亿美元,月产能约为100,000片。业界统计它的7纳米市占率近100%。

台积电的5纳米投资250亿美元,月产能50,000片,之后再扩充至70,000-80,000片。在2020年3月开始试产。同时2020的上半年它的6纳米进行风险生产,并将在2020年底进入量产。据台积电自述,预测2020年它的7纳米收入占比能达到30%,及5纳米的收入占比达10%。

台积电的3纳米计划,将于2020年开始建厂,2021年完成设备安装,并于2022年开始试产,及2023年正式量产,3纳米工厂的投资为200亿美元。

对于3纳米工艺技术路径,目前仅三星公布将采用GAA环栅的纳米片(Nanosheet)FET结构,而台积电是密而不宣,估计今年4月时才能公开。

因为从2011年英特尔推出3D finFET结构以来,延伸定律至14纳米,10纳米,至7纳米,一路平稳前行。而从7纳米工艺路线开始分岐。三星首先釆用EUV技术进入7纳米,试图扳倒台积电,但是“人算不如天算”,台积电仍坚持采用多次曝光技术先占领市场,它的策略奏效,取得几乎100%的7纳米市场。

进入5纳米,台积电也必须釆用EUV技术。但是市场预测5纳米可能与10纳米相同是个过渡节点,未来将迅速移向3纳米,但是在3纳米时现在的finFET架构已不再适用,导致市场开始“百花争艳”。

三星电子计划利用EUV工艺,提高在7纳米以下的市场份额。它的3纳米级技术计划首先应用在它的晶圆代工之中。三星计划2020年下半年在全球最先实现3纳米级芯片的批量生产。

三星电子将在最新的3纳米工程中使用新一代的工艺,称为“环栅架构GAA”。三星电子的半导体部门表示,基于GAA工艺的3纳米芯片面积可以比最近完成开发的5纳米产品面积缩小35%以上,耗电量减少50%,处理速度可提高30%左右。

3纳米制程是个坎,原因是之前釆用的finFET架构已经不再适用,需要釆用新的架构,统称为“GAA,环栅”,实际上它有多个选项,包括如Nanosheet,Forksheet及CFET等,因此尚需等样品产出经过测试后才能作出定论。这也是为什么台积电迟迟不愿公布它的3纳米架构的原因,一切可能尚在权衡之中。

业界预计3纳米是个与7纳米同样,长寿命节点,新的架构将影响下一步的2纳米,甚至1纳米工艺。

IBS的琼斯说,GAA在一定程度上提供了更佳的性能,与3nm的finFET相比,3nmGAA的阈值电压更低,潜在的功耗降低了15%到20%。但性能提升可能低于8%,因为MOL和BEOL是相同的。

纳米片FET和finFET的不同之处。finfet是用有限数量的鳍来量化的,给设计工作带来了一些限制,而纳米片的优点是它可以有不同的宽度。根据设计师的需要,它们可以更好的来权衡性能和功耗。

IMEC的Horiguchi说,最初纳米片有四层左右,典型的纳米片宽度为12nm到16nm,厚度为5nm。

台积电副总裁蔡晋(Jin Cai)在最近的IEDM演讲中表示:“纳米片FET面临的挑战是n/p不平衡、bottom sheet effectiveness、间隔层、栅极长度控制和device coverage。”蔡还讲到3nm和以下技术的趋势,但是蔡没有表示未来哪一种架构可能占优,也没有透露台积电的具体计划。

纳米片FET的工艺制程,首先在衬底上形成超晶格结构,然后用外延工艺在衬底上沉积硅锗(SiGe)和硅的交替层。每一个堆栈至少由三层SiGe和三层硅组成。

EUV设备

先进工艺制程持续推进,EUV技术起到非常关键作用。

EUV设备由荷兰ASML公司独家生产,每台设备约为1.5亿美元左右。EUV的光波长为13.5纳米,大大小于之前的氟化氩(ArF)激光波长(193纳米),可在不采用多次曝光成像的情况下绘制更加细微的半导体电路。而且这项技术还能简化成像工艺流程,因此目前被视为唯一的突破口。

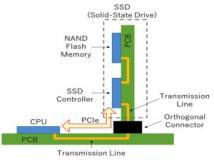

目前EUV技术主要运用在逻辑工艺制程中,台积电、三星及英特尔三家分摊60台订单。而对于存储器制造,据预测,NAND闪存不需要EUV,它通过提高堆垒层数来解决容量增大,现阶段3D NAND已达128层,有希望到200层,或者以上,对于DRAM,据预测在1x,1y及1z之后,将在15纳米左右,也要釆用EUV技术。已有报道三星于2020年底会把EUV技术纳入生产线中。

EUV光刻看似是一种工艺技术,然而它的使用涉及产业链,不仅工艺制程,尚包括设备,光刻胶,pellicle,无缺陷掩膜,缺陷测量等,因此需要时间上的积累。

到3纳米时,EUV技术除了要增大镜头的数值孔径NA,由0.33至0.55之外,同样也要加入多次曝光工艺。

据最新报道三星在2020年1月15日与ASML签订新的订单,将扩充采购20台EUV光刻机,总计花费33.8亿美元。

由于ASML的EUV设备市占率达100%,及每台价格达1.5亿美元左右,导致ASML可能超越应用材料公司,而夺得全球半导体设备销售的第一位。

EUV的应用从7纳米导入,经过5纳米,到3纳米时就需要EUV的DP(两次图形曝光技术),未来可能延伸至2纳米及以下,导致EUV的“生命周期”可能不会太长。

现阶段EUV技术尚需完善它的产业链,主要包括以下方面:

· EUV掩膜

EUV所用的掩膜和193nm浸液式光刻的掩膜完全不同,因为它是反射型光学系统。EUV的空白掩模由40到50层的硅和钼交替堆叠在衬底上构成,厚度250到350纳米。然而在叠层上沉积钌基覆盖层,紧接着再沉积钽基吸收体。

根据现有的数据,急需提高EUV掩膜的良率,因为传统的光学掩膜平均良率高达94.8%。它涉及光刻的成本问题。

· Pellicle薄膜

现在光学掩膜的pellicle薄膜是透明的,但是目前的EUV pellicle薄膜材料要求是不透明的,需要超薄型的薄膜材料去制造透明的EUV薄膜。目前ASML能提供50纳米的多晶硅薄膜作为pellicle,但是性能有待提高。据传目前台积电,三星釆用暂时不带pellicle工作,导致芯片生产线中必须经常的清洗和检查掩模,十分费时。

· 检测掩膜的缺陷

掩膜缺陷检测分为两类,die to die及die to database。从光学原理出发,最高分辨率在20-16纳米范围。Lasertec公司最近推出了一种能够检测20nm以下掩模缺陷的APMI(光化检测)系统。使用光化检测的优点之一是它的图像分辨率高。由于波长短得多,光化检查可提供高分辨率和高对比度的图像。目前该技术仍有待提高与完善。所以EUV的掩膜缺陷检查仍需时间的积累。

· 光源功率

据媒体报道,目前的250W光源应用在7纳米甚至5纳米时都是没问题的,然而到了3纳米,对光源的功率需求将会增大到500W,到了1纳米制程时,光源功率要求可能达到1,000W,是个不易解决的问题。

结语

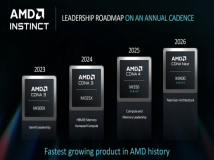

沿着定律工艺尺寸缩小仍在持续,台积电与三星两家在竞争,2020年5纳米开始量产,3纳米的研发已取得实质性进展,预计2022及2023年有望实现量产,它的客户主要是5G +AI及HPC等,包括苹果,华为,高通,AMD,Xilinx等。未来工艺尺寸缩小的主要问题可能不是技术因素,经济上的实用性才是主要阻碍。

定律除了工艺尺寸缩小外,尚有另外两个重要方向,包括异质集成以及新的架构与材料使用。可以充分相信在未来的十年中,即便尺寸缩小走到尽头,半导体业的前景仍是十分光明,因为它能持续地满足电子工业市场的需求。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。