利用该工艺可以自动测量自旋量子比特的工作点,并研究单个电子在全晶圆上的跃迁。

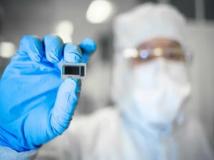

英特尔长期以来一直认为,利用其半导体制造实力和量子点量子比特的使用将帮助英特尔在提供实用量子计算的竞赛中成为领导者——英特尔量子硬件总监詹姆斯·克拉克(James Clarke)长期以来一直认为,这场竞赛将是一场马拉松。

5月1日,英特尔发布了一篇博客,概述了其实现这一目标的工艺进展,以及同日发表在《自然》杂志上的一篇论文(探测 300 毫米自旋量子比特晶圆上的单个电子)。

要点

- 英特尔代工技术研究部的量子计算研究人员开发了一种 300 毫米低温探测工艺,用于收集有关全晶圆上自旋量子比特器件性能的大量数据。

- 结果证明了自旋量子比特的最新均匀性、保真度和测量统计。

- 研究人员还发现,这些晶圆的单电子器件在作为自旋量子比特运行时表现良好,使用CMOS制造制造的量子比特的保真度达到99.9%。

英特尔代工技术研究部的量子计算研究人员开发了一种 300 毫米 (mm) 低温探测工艺,用于收集有关自旋量子比特器件在全晶圆上的性能的大量数据,从而获得最先进的自旋量子比特均匀性、保真度和测量统计数据。量子比特操作的更大均匀性可以减少大型处理器的控制线开销,使硅基量子计算机更接近于持续扩展和商业生产。研究人员还发现,这些晶圆的单电子器件在作为自旋量子比特运行时表现良好,使用互补金属氧化物半导体(CMOS)制造制造的量子比特的保真度达到99.9%。根据发表在《自然》杂志上的一项研究,高器件良率与低温探针测试相结合,提供了从器件制造到自旋量子比特研究的直接途径,消除了稀释冰箱阶段由于良率或静电引起的故障.

英特尔正在采取措施,通过改进三个因素来构建容错量子计算机:量子比特密度、均匀量子比特的可重复性以及来自大批量测试的测量统计数据。首先,英特尔的硅自旋量子比特比其他量子比特类型(如超导和俘获离子量子比特)更小、更密集,从而在芯片上实现更多的自旋量子比特。该公司的极紫外 (EUV) 光刻技术有助于实现这种密度,并结合设备上的大容量。其次,制造具有数百万个均匀量子比特的量子计算机需要高度可重复和可靠的制造。自旋量子比特利用英特尔的 300 毫米 CMOS 制造技术,该技术通常每个芯片生产数十亿个晶体管。第三,在CMOS制造领域开发大型量子计算机需要大容量的300毫米低温探测系统,以实现快速的过程迭代和学习。英特尔的整个测试过程(从对齐到设备测量)都是完全自动化和可编程的,与在低温恒温器中测量单个设备相比,将设备数据收集速度提高了几个数量级。

全晶圆低温测试功能的发展可以优化复杂的 300 毫米制造工艺,从而提高设备可靠性,从而实现对晶圆进行更深入的自动化测量。未来,这些进步可用于添加更多的互连层,以制造具有更多量子比特数量和连接性的二维阵列,以及使用CMOS工业技术制造高保真双量子比特门。

低温探测工艺

对于自旋量子比特,晶圆级探测需要进一步的冷却硬件,以达到低于 4 开尔文 (K) 的所需温度。低温晶圆探针是与英特尔合作开发的,由Bluefors和AEM Afore制造。低温探针可以在大约两个小时内将 300 毫米晶圆加载和冷却至卡盘处的 1 K 基温和约 1.6 K 的电子温度。冷却后,晶圆上数以千计的自旋量子比特阵列和测试结构可供测量。

图 1.在低温探针反馈的辅助下进行工艺优化。一个:优化的自旋量子比特阵列中的门结构示意图。设计用于积累电荷的栅极为黄色、蓝色和绿色,而用于消耗电荷的栅极(屏蔽栅极)为红色。b,c:通过优化栅极堆栈,改善了自旋量子比特器件的变化和静电性能。

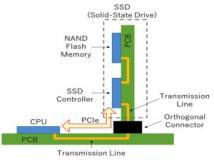

基于硅中电子的自旋量子比特显示出令人印象深刻的控制可靠性,但历来受到良率和工艺变化的挑战。为了实现高产量,研究人员使用了工业晶体管制造工艺的组合。量子点由平面架构定义(见图1)。用于受控堆积的主动门在单层中定义。在后来的器件中,还集成了用于筛选/耗尽的第二个无源层。栅极电极通过高介电常数复合堆栈(高 K 堆栈)与异质结构隔离,而相邻栅极则通过间隔堆栈隔离。

为了改善器件的差异性和性能,研究人员使用了两种方法——减少高 K 堆栈中的固定电荷和优化栅极层架构。高钾电堆中的固定电荷可能基于沉积的材料和条件,以及通过暴露于后续加工而产生。通过将间隔工艺的温度限制在生产线后端 (BEOL) 处理的典型热预算范围内,可以减少器件中的固定电荷。固定电荷的这些减少导致高K堆在较低温度下的结晶减少。此外,通过优化栅极堆栈,改善了自旋量子比特器件的变化和静电性能。

在工艺优化后,研究人员通过对具有 60 纳米 (nm) 栅极间距的 12 量子点 (12QD) 器件的测量来表征优化的工艺流程。测量是完全自动化的,以最大限度地提高数据收集的速度和一致性。12QD 设计由 12 个量子点组成的线性阵列和 4 个相对的传感器点组成,这些点由中央屏蔽门隔离。12 个量子点阵列可以作为各种自旋编码的物理量子比特运行,包括单自旋量子比特(在 12 量子比特阵列中)或仅交换量子比特(在四量子比特阵列中)。根据自旋量子比特编码,可以在设备中添加可选的微磁体层,中心屏蔽门可以提供微波电场,以电偶极子自旋共振来控制量子比特。

与CMOS逻辑过程一样,提高量子比特产量是扩展量子处理器的必要部分,因为更大的系统将依赖于越来越多的量子比特组件来运行。为了分析这种制造流程的良率,研究人员在晶圆上测试了12QD器件,并计算了欧姆接触、栅极、量子点和全12QD器件的元件良率。该测试方法提供了快速反馈,从而优化了CMOS兼容的制造工艺,从而实现了与领先技术节点的良率相称的低工艺变化和高良率。

使用低温探针进行大批量测试将继续实现工艺优化,以减少变化和无序,以及更高级的性能筛选(如电荷噪声、点间耦合和单电子跃迁紊乱),以确定量子计算应用的前沿测试芯片。总而言之,这些结果为当今自旋量子比特设备的规模和可靠性设定了新标准,为未来更大、更复杂的自旋量子比特阵列铺平了道路。

论文地址:https://www.nature.com/articles/s41586-024-07275-6

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。