英特尔首席执行官 Pat Gelsinger 详细介绍了如何需要先进的计算和封装来满足全球对计算的永不满足的需求,并在 Hot Chips 34 上实现完全沉浸式的数字体验。

8 月 21 日至 23 日,一年一度的 Hot Chips 34会议上,英伟达、Intel、AMD等巨头纷纷亮相,介绍或展示了各自在该芯片领域的成果。

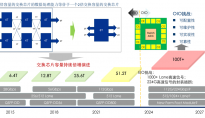

来自Intel官网内容,在 Hot Chips 34 上,英特尔重点介绍了支持 2.5D 和 3D 基于切片的芯片设计的最新架构和封装创新,这将带来芯片制造的新纪元,并在未来几年推动摩尔定律向前发展。 在自 1995 年戈登·摩尔 (Gordon Moore) 以来英特尔的第一个 Hot Chips 首席执行官主题演讲中,英特尔首席执行官 Pat Gelsinger 分享了公司继续不懈追求更强大计算的道路,并提供了公司即将推出的产品组合的详细信息,包括 Meteor Lake、Ponte Vecchio GPU、英特尔® Xeon® D-2700 和 1700 以及 FPGA,并概述了其新的系统代工模型。

“结合其他先进技术,如 RibbonFET、PowerVia、高 NA 光刻技术以及 2.5D 和 3D 封装的开发,我们的愿望是到 2030 年将封装上的 1000 亿个晶体管提高到 1 万亿个。从未有过更好的 - 或更重要的时刻——成为一名技术专家。 我们都必须成为半导体在当今生活中发挥的关键作用的大使。”

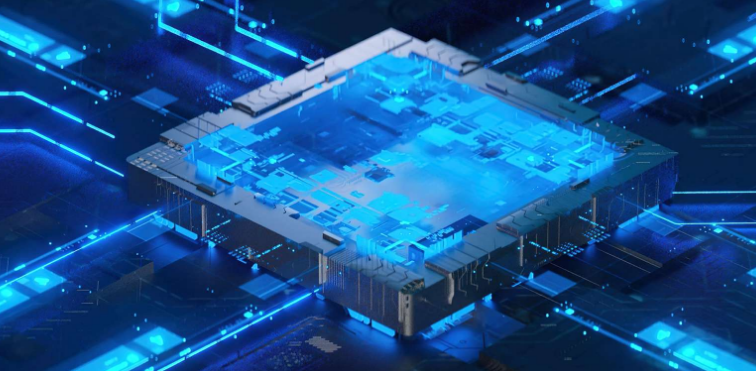

重要性: 该行业正在进入半导体的新黄金时代——芯片制造时代需要从传统的代工模式思维转变为系统代工。 除了支持传统的晶圆制造之外,英特尔的系统代工模式还结合了先进封装、开放式小芯片生态系统和软件组件,在一个封装中组装和交付系统,以满足世界对计算能力和完全沉浸式数字体验的永不满足的需求。 英特尔还通过工艺技术和基于块的设计的不断进步来满足行业需求。

在这个创新、增长和发现的时代,技术将从根本上改变我们体验世界的方式。 无处不在的计算、连接性、基础设施和人工智能将继续创造强大的新可能性,因为它们相互结合、放大和加强,塑造技术的未来并实现人类成就的新水平。

英特尔是如何做到的: 英特尔在 Hot Chips 34 上预览了来自下一代技术的以下产品架构:

- Meteor Lake、Arrow Lake 和 Lunar Lake 处理器 将通过基于 tile 的芯片设计改变个人计算机,从而提高制造效率、功率和性能。 这是通过使用英特尔的 Foveros 互连技术以 3D 配置堆叠的离散 CPU、GPU、SoC 和 I/O 块来完成的。 业界对开放式通用 Chiplet Interconnect Express (UCIe™) 规范的支持加强了这一平台转型,使不同供应商采用不同工艺技术设计和制造的小芯片在与先进封装技术集成时能够协同工作。

- 英特尔数据中心 GPU 代号为 Ponte Vecchio ,旨在解决高性能计算 (HPC) 和 AI 超级计算工作负载的计算密度问题。 它还充分利用了英特尔的开放软件模型,使用 OneAPI 来简化 API 抽象和跨架构编程。 Ponte Vecchio 由多个显示在瓷砖中的复杂设计组成,使用嵌入式多芯片互连桥 (EMIB) 和 Foveros 先进封装技术的组合进行连接。 高速 MDFI 互连允许封装扩展到两个堆栈,允许单个封装包含超过 1000 亿个晶体管。

- 至强 D-2700 和 1700 系列 旨在解决 5G、物联网、企业和云应用程序的边缘用例,特别考虑了许多现实世界实施中常见的功率和空间限制。 这些芯片也是基于 tile 设计的示例,包括最先进的计算内核、具有灵活数据包处理器的 100G 以太网、内联加密加速、时间协调计算 (TCC)、时间敏感网络 (TSN) 和内置用于优化 AI 流程。

- FPGA 技术 仍然是一种强大而灵活的硬件加速工具,尤其适用于射频 (RF) 应用。 英特尔通过集成数字和模拟小芯片以及来自不同工艺节点和代工厂的小芯片来确定新的效率,从而缩短开发时间并最大限度地提高开发人员的灵活性。 英特尔将在不久的将来分享其基于小芯片的方法的成果。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。