从 CPU 方面开始,据说新的 A15 具有两个新的 CPU 微架构,分别用于性能内核和效率内核。

几周前,我们看到 Apple 发布了他们最新的 iPhone 13 系列设备,这是一组由最新的 Apple A15 SoC 驱动的手机。今天,在我们将在不久的将来介绍的完整设备审查之前,我们正在仔细研究新一代芯片组,看看 Apple 在新芯片中究竟发生了什么变化,以及它是否符合要求炒作。

今年 A15 的发布在 Apple 的公关方面有点奇怪,特别是因为该公司通常避免在新设计与 Apple 自己的 A14 之间进行任何世代比较。特别值得注意的是,Apple 更喜欢在竞争环境中描述 SoC;虽然这在 Mac 方面并不罕见,但今年 iPhone 发布的情况比往年更加突出。

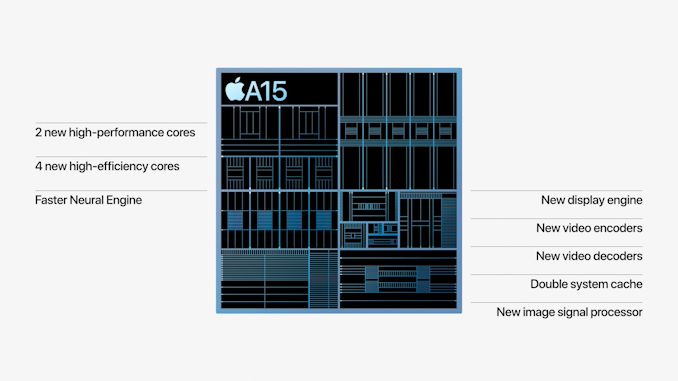

关于 A15 的几个具体事实是,Apple 正在为其 CPU 使用新设计、更快的神经引擎、新的 4 核或 5 核 GPU(取决于 iPhone 变体),以及全新的显示管道和视频媒体硬件块编码和解码,以及新的 ISP 改进以提高相机质量。

在 CPU 方面,改进非常模糊,苹果声称比竞争对手快 50%,GPU 性能指标也是这样制定的,描述 4 核 GPU A15 比竞争对手快 30%。,而 5 核变体的速度提高了 50%。我们已经完成了 SoC 的初始阶段,在今天的文章中,我们将重点关注新芯片的确切性能和效率指标。

频率提升;3.24GHz 性能和 2.0GHz 效率内核

从 CPU 方面开始,据说新的 A15 具有两个新的 CPU 微架构,分别用于性能内核和效率内核。关于新内核性能的前几份报告集中在频率上,我们现在可以在测量中确认:

| 最大频率与 每核加载的线程数最大 MHz |

||||||

| 苹果 A15 | 1 | 2 | 3 | 4 | ||

| 性能 1 | 3240 | 3180 | ||||

| 性能2 | 3180 | |||||

| 效率 1 | 2016 | 2016 | 2016 | 2016 | ||

| 效率 2 | 2016 | 2016 | 2016 | |||

| 效率 3 | 2016 | 2016 | ||||

| 效率 4 | 2016 | |||||

| 最大频率与 每核加载的线程数最大 MHz |

||||||

| 苹果 A14 | 1 | 2 | 3 | 4 | ||

| 性能 1 | 2998 | 2890 | ||||

| 性能2 | 2890 | |||||

| 效率 1 | 1823 | 1823 | 1823 | 1823 | ||

| 效率 2 | 1823 | 1823 | 1823 | |||

| 效率 3 | 1823 | 1823 | ||||

| 效率 4 | 1823 | |||||

与A14相比,全新A15将双性能核心集群的单核峰值频率提升了8%,相比上一代的2998MHz,现在达到了3240MHz。当两个性能核心都处于活动状态时,它们的工作频率实际上提高了 10%,与上一代的 2890MHz 相比,它们现在都以激进的 3180MHz 运行。

总的来说,鉴于很难推动设计的这一性能方面,Apple 在这里的频率增加非常激进,特别是当我们不期望新工艺节点方面的重大性能提升时。A15 应该是在台积电的 N5P 节点变体上制造的,尽管两家公司都没有真正透露设计的确切细节。台积电声称 N5 的频率增加了 +5%,因此对于 Apple 而言,如果超出这个范围,则表明功耗会增加,当我们深入研究 CPU 的功率特性时,请记住这一点。

A15 的 E 核心现在能够达到 2016MHz,比 A14 的核心增加了 10.5%。这里的频率与性能核心无关,因为集群中的线程数量不会影响其他集群,反之亦然。苹果对这一代的小核心做了一些更有趣的改变,我们稍后会谈到。

巨型缓存:性能 CPU L2 到 12MB,SLC 到大容量 32MB

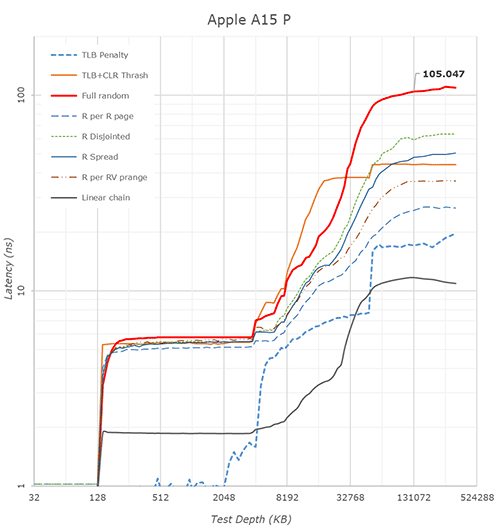

苹果在发布时透露的一个更直接的技术细节是,与 A14 相比,A15 现在具有两倍的系统缓存。两年前,我们详细介绍了 A13 的新 SLC,它从 A12 的 8MB 增加到 16MB,这个大小在 A14 代中也保持不变。Apple 声称他们已将其增加了一倍,因此这意味着 A15 中现在有 32MB。

看看我们对新 A15 的延迟测试,我们现在确实可以确认 SLC 现在已经翻了一番,达到 32MB,进一步推动内存深度达到 DRAM。Apple 的 SLC 可能是芯片能效的关键因素,能够将内存访问保持在同一个硅片上,而不是使用速度更慢、功率效率更低的 DRAM。我们已经看到更多 SoC 供应商采用了这些类型的最后一级缓存,但在 32MB 的情况下,新的 A15 使竞争对手的实现相形见绌,例如骁龙 888 上的 3MB SLC或 Exynos 2100 上估计的 6-8MB SLC .

Apple 没有透露的是,性能核心的 L2 缓存也发生了变化,现在已经从 8MB 增加到 12MB,增长了 50%。这实际上与 Apple M1 上的 L2 大小相同,只是这一次它只提供两个性能核心而不是四个。访问延迟似乎从 A14 上的 16 个周期上升到 A15 上的 18 个周期。

一个 12MB 的 L2 也是巨大的,与其他设计(例如 Snapdragon 888)的 L3+L2 组合(4+1+3x0.5 = 6.5MB)相比,增加了一倍多。很明显,Apple 在这方面投入了大量 SRAM年的 SoC 一代。

今年的效率核心似乎没有改变它们的缓存大小,保持在 64KB L1D 和 4MB 共享 L2,但是我们看到 Apple 已将 L2 TLB 增加到 2048 个条目,现在覆盖高达 32MB,可能会促进更好的 SLC 访问延迟。有趣的是,Apple 今年现在允许效率内核具有更快的 DRAM 访问,延迟现在约为 130ns,而 A14 上的延迟为 +215ns,再次在文章的下一个性能部分记住这一点。

CPU 微架构变化:缓慢的一年?

今年的 CPU 微架构有点像通配符。今年早些时候,Arm 宣布了新的 Armv9 ISA,主要由新的 SVE2 SIMD 指令集定义,以及该公司采用新架构的新 Cortex 系列 CPU IP。早在 2013 年,Apple 就因成为市场上第一个拥有 Armv8 CPU 的产品而臭名昭著,这是第一个支持64 位的移动设计。考虑到这种情况,我通常预计今年的一代也会推出 v9,但 A15 似乎并非如此。

在微架构上,A15 上的新性能核心似乎与去年的设计没有太大区别。我还没有花时间查看设计的每一个角落,但与 A14 性能核心相比,至少处理器的后端在吞吐量和延迟方面是相同的。

效率核心有了更多的变化,除了一些内存子系统 TLB 的变化,新的 E-core 现在获得了一个额外的整数 ALU,使总数从之前的 3 个增加到 4 个。无论如何都被称为“小”,而且今年似乎增长得更多,再次,我们将在性能部分展示。

苹果今年更温和的微架构变化的可能原因可能是几个因素的风暴——苹果在 2019 年明显地失去了他们在大型性能核心以及部分设计团队的首席架构师(Nuvia)(后来在今年早些时候被高通收购)。向 Armv9 的转变也可能意味着在设计上做了更多的工作,而大流行的情况也可能导致了一些非理想的执行。我们必须检查明年的 A16,才能真正确定 Apple 的设计节奏是否已经放缓,或者这是否只是一个滑点,或者只是下一个微架构发生更大变化之前的平静。

当然,这里的基调描绘了 A15 的 CPU 的相当保守的改进,在查看性能和效率时,它绝非如此。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。