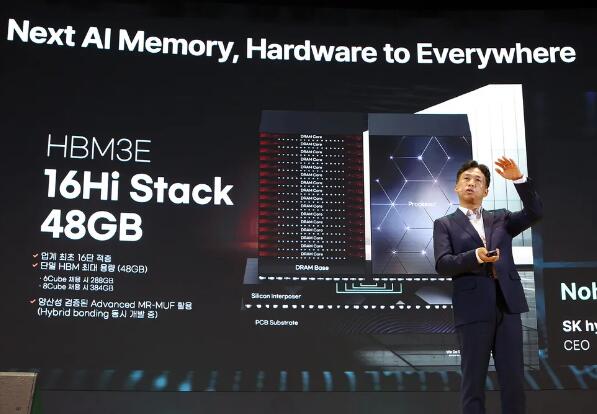

SK 海力士宣布推出全球首款 48GB 16Hi HBM3E 内存 — 下一代 PCIe 6.0 SSD 和 UFS 5.0 存储也正在开发中。

SK海力士最近在2024年SK AI峰会上发布了其HBM3e 16hi内存的开发,每个立方体的容量为48GB,计划于2025年上半年提供样品。这款新产品针对的是包括 CSP 的定制 ASIC 和通用 GPU 在内的应用。16hi HBM3e 产品有望在 HBM4 一代发布之前突破内存容量限制。

HBM 供应商传统上在每一代产品中引入 2 种堆叠高度选项 - 例如 HBM3e 的 8hi 和 12hi 堆栈,以及 HBM4 计划的 12hi 和 16hi 堆栈。虽然业内人士将于 2025 年下半年开始推出 HBM4 12hi,但 SK 海力士在 HBM3e 系列中增加 16hi 选项的举措可归因于几个关键因素。

首先,台积电的 CoWoS-L 封装技术有望在 2026 年至 2027 年期间支持更大的封装尺寸,从而允许每个 SiP 实现更多的 HBM 堆栈。然而,在超越这些计划的升级方面仍然存在挑战和不确定性。在生产要求更高的 HBM4 16hi 之前,HBM3e 16hi 为客户提供了高容量的选择。HBM3e 16hi 每个 SiP 具有多达 8 个 HBM 堆栈,每个系统可提供 384GB 的最大容量,大大超过了 NVIDIA 的 Rubin 的 288GB。

从 HBM3e 过渡到 HBM4 也会使 I/O 数量增加一倍。这推动了更高的计算带宽,同时增加了芯片尺寸,但每个芯片的容量仍为 24GB。在从 HBM3e 12hi 升级到 HBM4 12hi 的过程中,HBM3e 16hi 可以作为提供更低 I/O、更小芯片尺寸和更高内存容量的选项。

TrendForce 集邦咨询补充说,SK 海力士的 HBM3e 16hi 将采用先进的 MR-MUF 堆叠工艺。与 TC-NCF 工艺相比,MR-MUF 允许更高的堆栈数和更大的计算带宽。通过在 HBM4 的 16hi 版本之前生产 HBM3e 16hi,SK 海力士将能够积累宝贵的高堆栈制造经验,从而促进更顺利地过渡到 HBM4 16hi 的生产。SK海力士还在考虑未来发布使用混合键合的16hi版本,进一步扩展高级计算应用的高带宽选择。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。