RAID专利拥有者是IBM的Norman Ken Ouchi,在1977年提交了一项专利“SYSTEM FOR RECOVERING DATA STORED IN FAILED MEMORY UNIT”,中文:用于恢复故障存储单元中存储的数据的系统。

虽然RAID概念是由美国加州伯克利分校的David Patterson、Garth A. Gibson、和Randy Katz三人提出,但是RAID专利(专利号US4092732)属于Norman。1977年IBM的Norman Ken Ouchi提交了一项专利“SYSTEM FOR RECOVERING DATA STORED IN FAILED MEMORY UNIT”,中文:用于恢复故障存储单元中存储的数据的系统。其中涉及了磁盘镜像(RAID 1)、专用奇偶校验码(RAID 3和RAID4),这是后来的RAID 4的前身。

原文下载:SYSTEM FOR RECOVERING DATA STORED IN FAILED MEMORY UNIT。

图纸下载:Drawing pages of US4092732

以下为机器翻译,仅供阅读参考:

本发明涉及数据存储系统,尤其涉及用于恢复存储在已经发生故障的存储器单元中的数据的改进的装置。

背景技术

典型的数据处理系统通常涉及一个或多个存储器单元,其直接或通过控制单元和信道连接到中央处理器单元(CPU)。这些存储器单元的功能是存储CPU在执行给定数据处理任务时使用的数据和程序。

在当前数据处理系统中使用各种类型的存储器单元。存储器的响应时间和容量变化很大,并且为了最大化系统吞吐量,特定类型存储器单元的选择通常涉及其响应时间与CPU的响应时间及其对数据处理系统的数据存储需求的容量的匹配。为了最小化可能由慢速访问存储设备引起的对系统吞吐量的影响,许多数据处理系统采用许多不同类型的存储器单元。由于访问时间和容量也会影响存储成本,典型的系统可以包括快速访问小容量可直接访问的单片存储器,用于频繁使用的数据,以及一串磁带单元和/或一串磁盘文件,它们通过各自的控制单元连接到系统,用于较少使用的数据经常。后一单元的存储容量通常比单片存储器大几个数量级,因此数据的存储成本/字节较便宜。

然而,如果一个大容量存储器单元发生故障,使得该单元中包含的信息不再可用于系统,则存在问题。通常,这种故障将关闭整个系统。

现有技术提出了几种解决问题的方法。建议的最直接的方法是提供一组重复的存储设备或内存单元,并保留所有数据的重复文件。虽然这样的解决方案解决了这个问题,但它涉及重复存储成本,对系统性能有一些影响,因为对存储数据的任何更改都需要编写两条记录,还需要一些额外的要求,以便在主要事件中跟踪重复记录的保存位置记录不可用。

在一些系统中,当记录相对较小时,可以使用纠错码,该纠错码产生附加到记录的ECC校正子位。利用ECC校正子位,可以校正可能被错误读取的少量数据,但是这些数据通常不适合于纠正或重建错误或不可用的长记录。

现有技术提出的另一种解决方案涉及使用“校验和”。在该解决方案中,经受故障的一个存储器单元的内容将与经受故障的第二存储器单元的内容“异或”并且所得到的“校验和”存储在第三存储器单元中。这种布置具有优于双拷贝解决方案的优点,因为仅需要一个附加存储器单元。但是,每次在两个单元中的任何一个中更改数据时,必须生成新的校验和并在第三个单元上重写。这种布置可以扩展到多于两个单元,因为仅使用每个添加的存储器单元中的数据重复产生校验和的“异或”运算。

上述安排的缺点是,每次在一个单元中更新记录时,必须读取存储在校验和单元中的“校验和”并用旧数据“异或”,并用新数据“异或”。然后必须重写两个记录。如果存储器单元具有仅直接寻址要改变的记录的那部分和/或故障存储器单元具有非常小的容量的能力,则在系统吞吐量的影响方面的缺点相对较小。但是,如果响应系统的一条输入/输出指令传输到CPU或从CPU传输的数据量,或者存储在一个地址的记录长度很大,

在这种情况下,由于每次传输中涉及大量数据或者存储器单元不能处理较少量的数据,所传输的数据量需要相当长的时间来传输到存储器单元或从存储器单元传输,因此上面讨论的现有技术解决方案是不实用的商业解决方案

发明内容

根据申请人的安排,响应于一个CPU指令,在CPU和存储器之间正常传输大量数据的情况下,可以显着降低对系统性能的影响。在这方面,在申请人的系统中,要存储在存储器中的记录被细分为多个段,这些段至少比存储器单元的数量少一个。例如,如果有五个存储器单元,则记录被细分为四个相等长度的段。当记录被传送到存储器系统时,具有对应于记录段的字节长度的字节长度的“校验和”由每个传送段的“独占Oring”同时产生,其中系统记录的先前段导致最终的支票金额。记录段存储在彼此不同的故障独立存储器单元和“校验和”段上。由于校验和与将记录传送到系统或从系统传送的同时生成,并且仅涉及正在传送的记录,因此对系统吞吐量的影响最小化。由此减少了在记录改变时更新校验和的额外时间。通过在不同的故障独立单元之间分配记录段及其相关的校验和,如果一个单元失败,则在通过“独占Oring”将可访问段与其相应的“校验和”传输到系统期间,可以重建该单元上的段。 “ 分割。分割。由于校验和与将记录传送到系统或从系统传送的同时生成,并且仅涉及正在传送的记录,因此对系统吞吐量的影响最小化。由此减少了在记录改变时更新校验和的额外时间。通过在不同的故障独立单元之间分配记录段及其相关的校验和,如果一个单元失败,则在通过“独占Oring”将可访问段与其相应的“校验和”传输到系统期间,可以重建该单元上的段。 “ 分割。分割。由于校验和与将记录传送到系统或从系统传送的同时生成,并且仅涉及正在传送的记录,因此对系统吞吐量的影响最小化。由此减少了在记录改变时更新校验和的额外时间。通过在不同的故障独立单元之间分配记录段及其相关的校验和,如果一个单元失败,则在通过“独占Oring”将可访问段与其相应的“校验和”传输到系统期间,可以重建该单元上的段。 “ 分割。由此减少了在记录改变时更新校验和的额外时间。通过在不同的故障独立单元之间分配记录段及其相关的校验和,如果一个单元失败,则在通过“独占Oring”将可访问段与其相应的“校验和”传输到系统期间,可以重建该单元上的段。 “ 分割。由此减少了在记录改变时更新校验和的额外时间。通过在不同的故障独立单元之间分配记录段及其相关的校验和,如果一个单元失败,则在通过“独占Oring”将可访问段与其相应的“校验和”传输到系统期间,可以重建该单元上的段。 “ 分割。

因此,本发明的一个目的是提供一种改进的装置,用于从数据处理系统中的不可操作的存储器单元中恢复数据。

本发明的另一个目的是提供一种用于在多个存储设备上存储数据和校验和的装置,其允许在一个存储设备变得不可操作的情况下由系统恢复存储在设备上的数据。

本发明的另一个目的是提供一种改进的系统,用于在多个存储单元上存储数据记录和相关的校验和,这对系统吞吐量的影响最小。

本发明的又一个目的是提供一种改进的装置,用于通过校验和来恢复存储在不可操作的存储装置上的数据,其中产生和存储被传送到存储器的每个记录的校验和所需的时间减少到至少。

上述目的是在具有多个存储单元的存储系统中实现的,其中任何一个存储单元可能通过在多个单元和数据记录源之间提供具有缓冲器的校验和发生器和允许预定的适当控制电路而失败。记录段被传送到存储系统以与发生器并行供应。控制电路使校验和生成器在所有段上生成“校验和”,并将生成的校验和从缓冲器传送到没有存储任何记录段的存储单元。

因此,每个系统记录的记录段和相关校验和分布在不同的存储单元中。

从以下对本发明优选实施例的详细描述中,这些目的的实现方式将变得显而易见。

附图说明

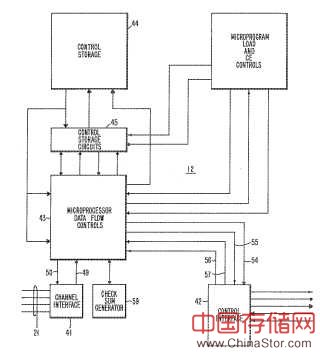

图1示意性地示出了可以容易地实现本发明的典型数据处理系统;

图2示出了图1中所示的控制存储单元的内部数据流和控制路径。1;

图3示出了图1的控制单元中采用的微处理器的细节。2;

图4示出了图4中的框图中所示的校验和生成器的细节。2;

图5示出了系统主存储器的一部分,示出了系统要处理的记录的存储位置; 和

图6示出了CPU用于跟踪记录段在物理上存储在磁盘驱动器上的位置的目录。

优选实施方案的描述

图1所示的系统包括:图1包括中央处理器10,其包括通道11,存储控制单元12,驱动控制器13和磁盘驱动器16-20的串14。存储控制单元12,驱动控制器13和串14可以称为存储子系统。CPU 10和通道11通过接口21连接到存储控制单元,接口21还可以将未示出的其他存储控制单元连接到系统。存储控制单元12通过接口22连接到驱动控制器13,接口22还可以将其他驱动串连接到控制单元。驱动控制器13通过接口23连接到驱动器16-20。

在优选实施例中,CPU是通过通常的I / O接口连接到IBM 3830-2存储控制单元的IBM System / 370模型168。3830-2连接到IBM 3333磁盘文件模型A2,其包括驱动器控制器13和磁盘驱动器16和17.接口22是控制器接口的通常控制单元。驱动器18-20代表一个3330型号B2磁盘驱动器和一个3330 B1磁盘驱动器。所有驱动器都通过通常的IBM CUDI接口连接到控制器。

标准3830-2存储控制单元如图1所示。图1中所示的附加硬件与图1所示的附加硬件相结 图4实现了本发明。有关3830-2存储控制单元及其接口的结构和操作的详细信息,请参阅IBM公司的IBM维护出版物“3830-Storage Control-Model 2”版权所有1973,以及IBM出版物“参考手册”。 IBM 3830存储控制 - Mod.2,出版物GA26-1715“最初版权于1972年。

以块形式显示的单元的功能及其相互关系在本领域中通常是众所周知的,因此,将仅简要概述。

在图1所示的系统中,如图1所示,在问题状态下在CPU内执行需要逻辑和算术决策的操作。对于I / O操作,CPU必须处于监控状态。响应于程序启动的监督调用指令或者当设备启动的中断发生时,CPU从问题变为监控状态。当处于监控状态时,CPU可以执行许多I / O指令,例如启动I / O,暂停I / O和暂停设备。I / O指令的格式包括一个用于定义操作代码的字节和两个用于定义通道地址,存储控制地址和设备地址的附加字节。

通道根据通过合适的应用程序在CPU存储器中设置的一串通道命令字(CCW)直接控制I / O设备和存储控制。例如,在通道收到启动I / O命令后,它将获取通道地址字(CAW),它是位于CPU主存储器中指定位置的四字节字。该字的三个字节用于定义位于主存储器中的CCW链中的第一个CCW的地址。

通道从CAW指定的地址获取第一个CCW。CCW的长度为8个字节。一个字节用于定义特定命令,三个字节用于主存储器中涉及操作的存储地址,两个字节用于定义要涉及的主存储器中的字节位置数。在接收到CCW之后,通道选择通过将地址发送到所有连接的存储控制单元而指定的设备。如果单个设备可用,则CCW的命令代码被发送到存储控制单元,该单元向信道返回初始状态字节。如果设备忙,则会向CPU发送信号,并在短时间后再次发出命令。

存储控制单元可以通过激活第一CCW中的预定义位,从单个启动I / O指令执行一系列CCW。下一个CCW会自动获取。此功能称为命令链接。

在CPU主存储器和驱动器之间传输的数据也可以链接。这允许当数据块位于非相邻的CPU存储位置时传输数据块。CCW链中的下一个CCW通常取自高于当前CCW的地址八个存储地址,除了在“搜索”命令中提供如果搜索成功则跳过一个CCW。“在信道中传送”命令(TIC)指定下一个CCW的主存储位置。可以在任何有效的CPU存储位置中指定下一个CCW。上述两条指令规定了CCW链中的有限分支能力。存在几种不同类型的CCW,并且可以从该信道发送。

控制命令

控制命令不涉及存储控制和主存储之间的数据记录传输。但是,在某些操作中,控制字节从主存储器传输到存储控制器。

搜索命令

在执行搜索命令期间,通道以写入模式运行,而磁盘存储器以读取模式运行。存储控件将来自主存储器的数据与来自驱动器的数据进行比较。当满足搜索要求(例如,比较相等,高等)时,存储控制返回具有信道结束和设备结束指示符比特的状态修改符比特。该位使得信道跳过链中的后续CCW,并从高于当前CCW的存储位置16地址获取下一个命令。

每个搜索命令一次对一个记录进行操作。要搜索另一条记录,必须重新发出该命令。这通常通过将TIC命令“transfer-in-channel”链接到搜索命令来完成,如下所示:

Search Key Equal

Tic * -8

读取数据;如果搜索不成功,则“搜索”命令后面的TIC命令会导致搜索重复。搜索成功时,状态修饰符将跳过TIC命令并执行读取数据命令。; READ COMMANDS;读取命令将信息从磁盘存储器传输到中央处理单元。读取命令可以在单轨道或多轨道模式下操作。;在所有读取命令上,检查附加到要读取的记录的纠错码字节,以确定每个记录区域在传输时的有效性。在检查校正码字节并建立数据有效性之后,存储控制将信道端和设备端的结束状态字节发送到信道。; WRITE COMMANDS;写命令有两种类型,格式化和更新。; 格式化写入命令;格式化写入命令初始化和写入轨道和记录,并确定每个记录中区域的长度。在每个记录区域之后计算并写入纠错码字节。;格式化写命令是:

写入家庭地址

写入RO

写入计数,密钥和数据

写入特殊计数,密钥和数据

擦除。;更新写入命令;更新(非格式化)写入命令用于更新现有记录,并且必须在先前格式化的轨道上操作。; Update Write命令是:

写入数据

写密钥和数据。; SENSE I / O / TEST I / O命令;这些命令用于确定3830-2设施的状态,并识别已发生的任何特定错误或异常情况。;当通道需要状态信息或处理测试I / O指令的结果时,通道自动生成测试I / O命令。在任何一种情况下,它在存储控制中看起来都是全零的命令字节,并被视为立即命令。测试I / O请求存储控制将所有未完成的状态信息发送到通道,并且通常呈现全零状态字节。sense I / O命令将7个字节的数据传输到通道,以识别所选单元的存储控制和设备类型。除了通常用于图1所示类型的系统的标准CCW之外,还可以使用标准CCW。1,几个新的CCW用于本发明。将结合图4解释这些CCW及其功能。结合图1所示系统采用的各种CCW的更详细描述。可以在先前引用的IBM出版物“IBM 3830 Storage Control的参考手册 - Mod.2,Publication GA26-1715”中找到图1中所示的内容。控制器13和磁盘驱动器16-20在图1中显示为单独的单元。实际上,这些单元的包装确实变化,使得控制器13和磁盘驱动器16和17可以封装为一个单元,驱动器18和19作为另一个单元等。出于解释的目的,控制器13和驱动器16。 -20被确定为IBM 3330系列类型驱动器,也可以使用IBM 3340系列或IBM 3350系列或其他系列。用于各种系列的驱动控制器13在细节上不同,但是到控制单元的接口22和到每个驱动器的接口23通常保持相同。控制器的整体功能是从存储控制单元接收命令,这些命令使得来自通道的启动I / O命令选择的驱动单元存储数据或读取先前存储的数据。如前所述,通道的启动I / O命令包括一个双字节字段,用于定义存储控制单元和特定驱动器的地址。在安装时为控制单元和驱动器分配特定地址。磁盘驱动器上的磁道由柱面编号(CC)和磁头编号(HH)定义,而磁道上的记录由记录编号(RN)定义。当每个记录进入系统时,在主存储器的CPU中建立一个目录,该目录根据要存储数据的驱动器号,气缸CC,磁头HH和记录RN来识别。此外,系统还维护记录的长度,以字符数或字节数表示。应用程序使用该信息构建CCW链,该CCW链控制存储系统和CPU之间的数据传输。还应该理解,每个磁盘驱动器的磁道格式是计数密钥数据格式,它是业界磁盘驱动器的通常数据格式。今天在本领域中很好地理解在磁盘驱动器和CPU之间传输数据的功能。可以在先前引用的IBM出版物和其他IBM出版物和专利中找到对特定硬件及其操作的详细描述。为了更好地理解本发明的优选实施例,将结合图3和图4概括地描述存储控制单元的操作。如图2和3所示。如图2所示,存储控制单元12包括通道接口电路41,控制器接口电路42,包括控制存储器44的微处理器43和用于控制存储器44的控制电路45。如图2所示,来自信道的数据被提供给线路49上的微处理器,而来自微处理器的数据被提供给线路50上的信道。从微处理器到控制接口42的输出包括数据输出总线54和控制线55.从控制接口42到微处理器的输入包括数据输入总线56和控制线57.从微处理器提供给微处理器的命令数据。在控制单元中对信道进行解码,并且根据命令的类型,与微程序协作的解码信号在微处理器内部或控制器接口42上设置适当的数据流路径,以使命令被执行。类似地,从驱动器通过控制器接口42提供的状态类型信息使微处理器分支到适当的微程序子程序。参考图1的微处理器电路。3,通过微程序将要从通道记录在选定驱动器上的数据放入寄存器TA中,然后在微程序控制下一次一个字节地传送到控制器。类似地,从要传送到主存储器的文件读取的数据被放置在寄存器MA中,并且随后通过通道接口41一次一个字节地传送到CPU。在先前引用的IBM出版物中详细阐述了控制各种微处理器可寻址寄存器以传输数据和控制信号的方式。在图3和图4中以方框形式示出的校验和生成系统59的细节。图2中示出了图2和3。4.;图4中所示的校验和生成器59。图4包括4,096字节缓冲器60,缓冲器输入寄存器61,缓冲器输出寄存器62,缓冲器寻址电路63和缓冲器控制控制逻辑64.通过控制单元提供给文件的数据也通过与门65,或门66和异或门67提供给缓冲器。通过控制从文件读取数据。单元也通过与门68,或门66和异或门67提供给缓冲器输入寄存器。输出缓冲寄存器62连接到寄存器MG,寄存器MG的功能类似于寄存器MA和TA,用于将缓冲器中的数据传送到CPU。或驱动器。异或门67的一个输入也通过与门69连接到输出寄存器62,使得异或门67产生校验和字节。还提供附加寄存器MH70,以在微处理器的控制下产生控制信号CTL10-CTL14。; 缓冲器控制逻辑64用于控制缓冲器读取周期和缓冲器写入周期,并使缓冲器的操作与通过微处理器的数据传输同步。当记录的4,096字节段传输到驱动器时??,校验和生成器自动生成校验和。然后将最终校验和信号传送到适当的驱动器。在重建由于其中一个驱动器变得不可操作而变得不可用的记录段时,记录的可用段被传送到CPU系统和校验和生成器。校验和段也被传送到生成器,这导致重建不可用的系统记录段。然后通过MG寄存器将重构的段读入适当的存储区,系统继续以正常方式处理记录。;图2所示系统的操作。现在将描述图1。出于解释的目的,假设系统处理的每个记录的长度为16,384字节长,并且每个记录被分成四个段,每个段的字节长度为4,096字节。因此,校验和段也是4,096字节。进一步假设每个存储设备上的轨道具有存储3个4,096字节的三个段的容量。系统记录分成四个4,096字节的段由系统在应用程序的控制下执行,该程序将物理存储位置分配给系统记录。这样的程序通常涉及建立识别系统记录及其物理位置的目录。典型的目录如图2所示。如图所示,系统记录SRO的段S1到S4被分配给相应的驱动器000003.在这种情况下,每个段被分配一个相应的驱动器的相同轨道,并且是该轨道上的第一个记录。校验和段被分配给相应的轨道和记录地址的驱动器004。该表由应用程序用于构造通道命令字链,其控制与存储子系统之间的数据传输。进一步假设应用程序使用指定的存储区域作为在传输到存储子系统之前存储系统记录的位置,并且相同的区域用于存储从存储子系统读取的系统记录。如图1所示。在图5中,为了解释的目的而分配的存储器地址是00000到16,384,使得来自驱动器000的记录段存储在存储器位置00000到04095,来自驱动器001的段存储在存储器位置04096到08191等处。图1所示的系统。现在将使用上述假设来描述与系统记录到存储子系统的初始传输有关的图1。;第一个系统记录到存储子系统的传输开始于系统向通道发出启动I / O指令。Start I / O指令包含指定存储设备的地址,在本例中为000。成功执行Start I / O指令建立了从寻址驱动器到系统的连接,并导致先前建立的CCW链被发布到存储子系统。CCW的链条如下:

(1)搜索

(2)搜索ID

(3)tic * 8

(4)写入并初始化缓冲区。

CCW的1 - 3是旧的,将在功能上进行描述。CCW 4在功能上作为传统的“写入”CCW运行,除了与校验和发生器有关。详细解释了这种关系。

“Seek”命令的功能是将五个字节的地址信息传送到驱动器,以将Start I / O指令选择的驱动器的访问机制定位到正确的柱面,在这种情况下,柱面是柱面01和选择寻址的磁头,它有效地选择驱动器000上磁道的假想圆柱01中的一个磁道01.实际上,在发出“寻找”指令并执行其他功能之前,通道将断开,直到存储子系统通知访问操作是完成后,重新建立驱动器与系统的重新连接。

然后发出“搜索ID”CCW,它将相同的五个字节的信息CC,HH,R1传送到控制单元。控制单元通过微处理器向驱动器发送适当的指令,以使先前在轨道上格式化的记录ID字段被读取并提供给控制单元,在那里将其与从系统提供的五字节字段进行比较。如果比较导致不等式,则发出以下“TIC-8”CCW,这导致重新发布先前的“搜索ID”CCW。由于轨道先前已被格式化为包含三个每段4,096字节的段,因此每个轨道的格式为ID对应于记录R1至R3。“搜索ID”的次数 重新发布CCW将取决于在记录开始读取时相对于头部所寻找的ID字段的位置。通过在“搜索ID”命令之前使用“设置扇区”命令,该旋转等待时间可以与其他操作重叠,但是为了简化说明,将不再描述。

在存储控制单元检测到成功的比较操作时,下一个CCW“写入和初始化缓冲器”被发送到控制单元。

这个CCW的功能是双重的。第一个功能是使系统记录的第一段存储在缓冲区中。因此,提供给控制单元的信息包括存储第一段开始的amin存储器中的地址,即主存储地址00000.提供给存储控制单元的其他信息是要写入的字节数,其中这个例子是4,096。该功能与传统的“写入数据”CCW相同。另外,微处理器对CCW的解码使得数据的控制字节从微处理器的控制存储器中的位置传送到图1和2中的MH寄存器70。2和4。该控制字节的所选位用于控制缓冲器的输入并使其操作与微处理器的操作同步,如图4所示。4.如前所述,缓冲器的输入源自TA寄存器,TA寄存器位于驱动器的主数据路径中。通过用来自MH寄存器的控制CTL 11信号调节AND门65,建立到输入寄存器61的数据路径。类似地,通过提供NOT控制CTL 12信号以禁用AND门69,异或门的另一输入67也被禁用。通过向缓冲器控制逻辑64提供控制信号CTL 14,将传送到驱动器的记录的第一段存储在缓冲器60中。在为该段传送的数据的最后一个字节完成时,存储控制单元与通道断开连接,系统发出另一个选择驱动器001的启动I / O指令。此应用程序已构建类似于第一个CCW链的第二个CCW链,但核心存储器中的不同地址除外。第二个段的开始,在这种情况下将是04096.第二个CCW链被进一步修改为采用“写入和生成CHECK SUM”CCW而不是“写入和初始化缓冲区CCW”。写入和生成CHECK SUM CCW以前述方式起作用,除了CTL 12被激活并且反馈路径通过异或电路67建立,因为AND门69被配置。通过与门69和异或电路67反馈的输出缓冲寄存器62的输出实际上是 记录的第1段。结果是在段2到驱动器001的传输结束时,缓冲器包含表示段1和2的异或的总和的中间校验和。段3和4的传输操作与连接中描述的相同。传输操作结束时的缓冲器60包含要记录在磁盘驱动器004,柱面01和磁头01上的记录位置R1的校验和。

在系统和驱动器004之间建立连接的启动I / O指令包含CCW链,其类似于先前的链,除了最后的CCW是“写校验和缓冲器”CCW。当由微处理器解码时,该CCW有效地将MG寄存器替换为通常用于以串行方式向控制器13提供数据字节的TA寄存器(图3)。在MH寄存器中还放置一个不同的控制字节,以便为缓冲器寻址设置适当的控制到缓冲器控制逻辑64。从系统传送到存储控制单元的虚拟字节的数量与先前的传送一样保持跟踪,以便当接收到4,096个虚拟字节时,存储控制单元发信号通知操作的结束。这些字节不会记录在驱动器中,而是

存储子系统以相同的方式加载剩余的系统记录。每个系统记录中只有一个段存储在驱动器上,该系统记录的校验和存储在不同的驱动器上。如上所述,校验和全部存储在驱动器004上,而每个系统记录的相应段存储在同一驱动器上。本领域技术人员将认识到,其他段分配系统也是实用的,唯一的要求是与系统记录相关联的每个段存储在不同的驱动器上。还应该理解,如果需要,可以在一个驱动器上存储两个段,条件是还产生两个校验和。例如,如果将系统记录划分为8个段,并为每个段生成校验和,

在正常情况下,校验和段永远不会读入CPU当CPU要更新或更改给定记录时,当更新的系统记录被传输到存储子系统时,会同时生成新的校验和支票金额只是在旧的支票金额上重写。在不首先读取旧校验和的情况下改变记录并同时产生新校验和的能力是优于现有技术布置的重要优点,因为对系统性能的总影响保持最小。

应当理解,用于将记录转移到存储器中的CCW链不一定以所描述的串行方式执行。例如,在给出第一个链中的Seek命令之后,可以发出其他四个Seek命令。换句话说,CCW链可以并且通常在这样的操作中交错,而不影响给定系统记录的校验和的最终值。

图9中所示的校验和生成器的操作包括:现在将结合读取操作来描述图4,特别强调在一个驱动器变得不可操作并且系统记录的记录段不可用的情况下系统的操作。

响应于“读取数据”从所选驱动器向系统读取数据CCW从控制器传送到微处理器的MA寄存器,然后传送到系统。如图1所示。如图4所示,来自串行器 - 解串器的MA寄存器的输入也被馈送到AND门68,使得被读取的数据也通过OR门66,异或门67和缓冲器输入寄存器61,AND门同时馈送到缓冲器60。先前已经通过合适的控制信号CTL 10从MH寄存器70启用68.在第一段被传送到系统之前,缓冲器60被清除或者AND门69被适当的控制信号而非CTL 12禁用。当AND门69被使能时,产生中间校验和。如果其中一个驱动器不起作用,则“检查总和” 然后将存储在驱动器004上的该记录读入系统并提供给缓冲器。此时缓冲区中的数据表示系统记录中无效驱动器上不可用的段。然后,响应于“向系统的读缓冲器”CCW,重构的段通过MG寄存器从缓冲器60传送到系统。重建的数据存储在存储器中与分配给原始段的位置相对应的位置。

如前所述,缓冲器控制逻辑64的功能是使缓冲器的操作与微处理器的正常操作同步,使得微处理器在驱动器和系统之间传输的数据也以同步的方式进入和离开缓冲器。 。

缓冲器60例如由计数器80寻址,计数器80通过施加来自MH寄存器的CTL 13信号而被初始化为全零,并且由来自缓冲器控制逻辑的线81上的输出信号步进。缓冲器60的读周期和写周期由来自缓冲器控制逻辑64的线82和83控制。读周期将一个字节从缓冲器传送到输出寄存器62,并且写周期从输入寄存器61传送一个字节到缓冲区。这些周期是交错的,使得对于任何一个寻址位置,首先将数据传送到输出寄存器62,然后将输入寄存器61中的数据传送到寻址位置。然后,地址计数器被步进,并且响应于来自逻辑门??85的“下一个”信号84重复循环。

逻辑门85响应于线86上的“设置ST4”信号或“线路87上的MG信号取出”提供“下一个”信号。“设置ST4”是响应于控制单元中通常产生的信号。驱动器或系统向控制单元发送“同步”信号,表示它已经接收到一个字节的数据,并且可以发送另一个字节。

当重建的段是微处理器时,微处理器产生“取MG”信号。被转移到系统以响应“读取缓冲区到系统”。

虽然已经在具有微处理器的控制单元的实施例中公开了本发明的校验和产生装置,但是对于本领域技术人员来说显而易见的是,与校验和发生器相关的微处理器的功能可以是在固定硬件中实现,而不影响校验和生成器或故障独立存储设备之间的段分配的基本操作。此外,将本发明应用于多级存储环境的优点应该是显而易见的。还应该注意的是,虽然存储驱动器已被描述为磁体12磁盘存储驱动器,但是可以采用其他类型的存储驱动器而不脱离本发明的精神或所附权利要求的范围。

更多RAID相关知识请访问:RAID知识大全

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。